EEE40002: Integrated Circuit Design Assignment, SUT, Malaysia Ability to evaluate the CMOS transistor characteristics and Conduct investigations of complex problems using research-based knowledge

| University | Swinburne University of Technology (SUT) |

| Subject | EEE40002: Integrated Circuit Design |

This assignment covers:

Ability to evaluate the CMOS transistor characteristics. Conduct investigations of complex problems using research-based knowledge (WK8) and research methods including design of experiments, analysis, interpretation of data, and synthesis of the information to provide valid conclusions.

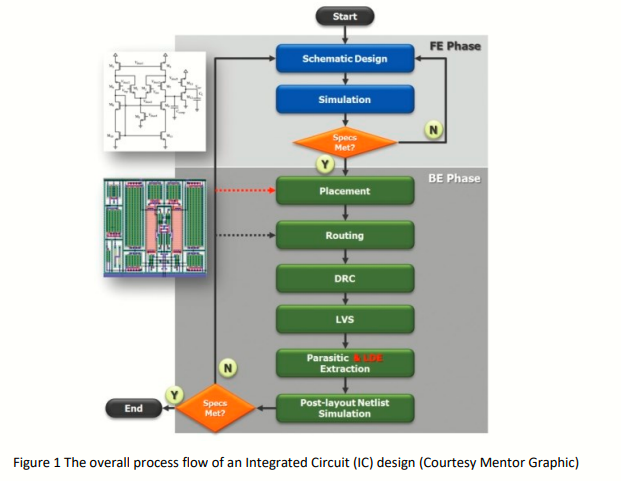

Figure 1 shows the overall process flow of an Integrated Circuit (IC) design.

SULIT

The operation begins with Front End Phase by creating the transistor-level schematic design based on the design specifications, before proceeding with the simulation step. In this simulation step, the test benches are required to verify the functionality of the design.

Next, the operation continues with Back End Phase by designing the layout based on the schematic design. Several steps are involved in this layout design phase such as Pre-layout design which includes Placement and Routing steps. Layout designers can always try different device placements and examine

the impact of any specific configuration of device placement on the original specification. Then, the process continues with DRC (Design Rule Check) and LVS (Layout Versus Schematic) steps. A successful DRC ensures that the layout conforms to the rules designed for faultless fabrication, while the successful LVS ensures that the layout connectivity of the physical design matches the schematic design.

Students in NMJ216043 was exposed to all the design process mentioned earlier. However, to achieve a successful post-layout design that meets all the specifications, important tasks like parasitic extraction is required. Students should be aware that the behavior of the layout design is extremely sensitive to the layout-induced parasitics such as inductance, resistance, and capacitance. Parasitics not only influence the layout performance but often render it non-functional. Hence, it is essential to consider the effect of parasitics in the design process. In conclusion, the major purpose of parasitic extraction is to create an accurate layout of a circuit, so that the simulations can emulate the actual circuit responses.

Get Help By Expert

Experience top-notch assistance for your Integrated Circuit Design assignment at Swinburne University of Technology. Explore Assignment Helper My, your dedicated partner for academic success. Our Malaysia-based online assignment helpers bring comprehensive insights and guidance to ensure your project's excellence. You also acquire our professionals for the best Online Exam Help.

Recent Solved Questions

- MPRM7113 RESEARCH METHODOLOGY SEPTEMBER 2024 SEMESTER

- A firm must choose from five capital budgeting proposals listed below. The firm is subject to capital rationing: principle of finance Assignment, UOW, Malaysia

- PHT485 Exercise Physiology Assignment: Exercise Recommendations for Managing Hypertension

- DCP5101: Program Design Assignment, MMU, Malaysia I need a standalone console application that can keep track of my restaurant sales. Customers will typically order food and drinks

- Operations Management Assignment, MU, Malaysia Oral cancer represents the sixth most common malignancy in the world. There are a lot of oral cancers depending

- Unit 1 Strategic Supply Chain and Logistics Management Assignment Malaysia

- International Building Control Report, TARC, Malaysia Human effort in the organization is indispensable. It constitutes a complex phenomenon for managers of such organizations

- Computer Science Assignment, UON, Malaysia A floating bottle has two ways to go: either it goes to someone else or it comes back to you. The floating bottle

- Supply Chain and Operations Strategy Assignment | International College of Business & Technology

- FIN30014: Financial Risk Management Case Study, SUT, Malaysia Industrial commodities in China mostly rose as the number of Covid-19 cases fell and the government began to loosen the restrictions